# RISC-V®

# RISC-V Vectors & oneAPI Accelerating the Future of Heterogeneous Compute

Stephano Cetola, Director of Technical Programs

### What is **RISC-V**?

## Who is RISC-V

RISC-V International is a global nonprofit association based in Switzerland. Founded in 2015, RISC-V brings together 3k+ members in more than 70 countries across industries and technical disciplines.

RISC-V supports the open RISC-V instruction set architecture, developing additional extensions, tools, and resources paving the way for the next 50 years of computing design and innovation. RISC-V also connects the community and industry through academia, commercialization, and strategic leadership.

#### Building Hardware using RISC-V

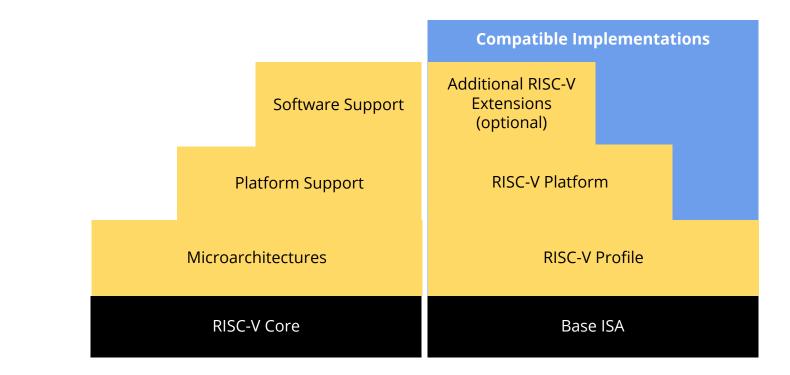

### Standardization, Modularity, and Flexibility

General and differentiated software **Open software** Applications, Linux support, libraries/platforms Expertise, applications, services Academic + Research General and differentiated implementations IP, SoC, FPGA, enhanced functions implementations Open standard Commercial **IP** specifications innovation and Open design tools + Leading industry design tools + software for modular differentiation to software Compilers, Simulators, Tools, designs based solve full on decades of spectrum of investment and Commercial IP and cores compute **Open IP and cores** challenges expertise Provided via ecosystem for differentiated performance and capabilities Modular IP specifications + Architecture compatibility tests Profiles, extensions incl Vector, Security, Memory, Trace + Debug RISC-V Instruction Set Architecture (ISA) Open Standard

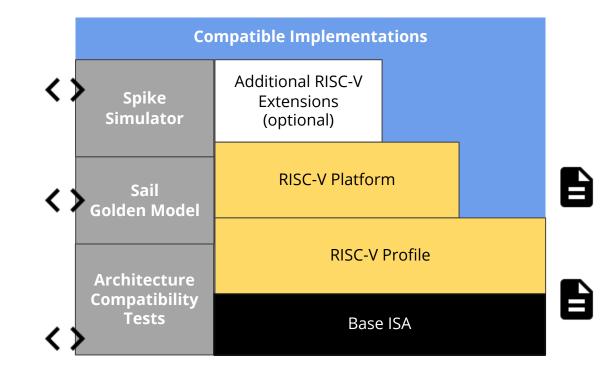

### Hardware Compatibility using RISC-V

- > Profiles

- > Platforms

- > Sail Golden Model

- > Architecture Tests

- > Spike Simulator

- = Specification Document

- ♦ > = Open Source Code

## Who is using **RISC-V**?

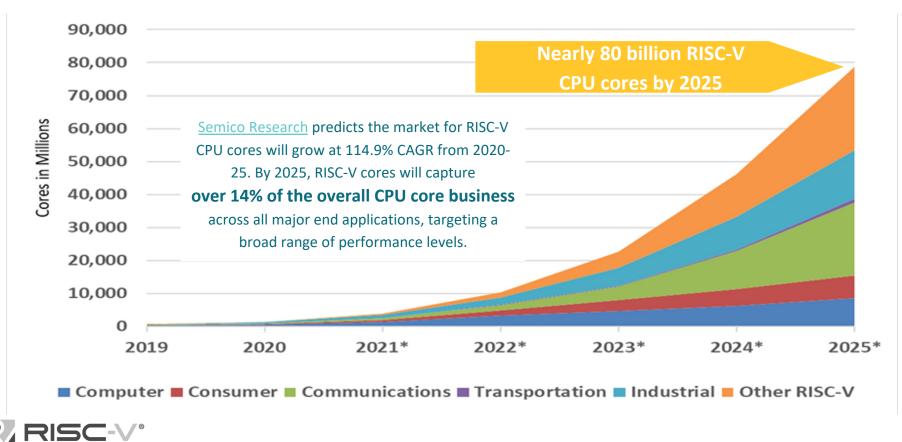

### **Rapid RISC-V Growth**

#### More than 3,100 RISC-V Members across 70 Countries

RISC-V°

| 3200                            | 111 Chip<br>Soc, IP, FPGA                                                                 | 3 Systems<br>ODM, OEM                                                                                  |  |

|---------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| 2800                            |                                                                                           |                                                                                                        |  |

| 2400                            | 3 I/O                                                                                     | 14 Industry                                                                                            |  |

| 2000                            | Memory, network, storage                                                                  | Cloud, mobile, HPC, ML, automotive                                                                     |  |

| 1600                            |                                                                                           | 100 D                                                                                                  |  |

| 1200                            | 19 Services                                                                               | 139 Research                                                                                           |  |

|                                 | Fab, design services                                                                      | Universities, Labs, other alliances                                                                    |  |

| 800                             | And a                                                                                     |                                                                                                        |  |

| 400                             | 56 Software                                                                               | 2k+Individuals                                                                                         |  |

| 0                               | Dev tools, firmware, OS                                                                   | RISC-V engineers and advocates                                                                         |  |

| Q3 Q4 Q1 Q<br>2015 2015 2016 20 | 2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4<br>16 2016 2016 2017 2017 2017 2017 2018 2018 2018 2018 2 | Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4<br>2019 2019 2019 2019 2020 2020 2020 2020 |  |

| Oct 2022                        |                                                                                           |                                                                                                        |  |

**RISC-V** membership rapid growth of 134% in 2021

### Data Center Cloud, HPC

Top providers like Amazon and Alibaba are designing their own chips.

New features specific to HPC such as Vector and larger Virtual address space

#### Automotive

Transforming from autonomous vehicles to infotainment to safety, the whole vehicle relies on innovative electronics.

#### AI / ML

Artificial intelligence is incorporated across many areas including Industrial IoT, manufacturing, and financial

((( o )))

#### Telecom & Communications

Rapid evolution in 5G, handsets, and base stations grows with each generation of hardware and increased capability

#### Consumer and IoT devices

Incredible innovation is driving volume with billions of connected devices in the next 5-10 years.

####

A distributed, open architecture decentralizes processing power, reduces latency, and supports IoT performance in low bandwidth environments. RISC-V adoption spans industries

#### RISC-V will capture 10% of the Automotive market by 2025

- Counterpoint, September 2021

- **MobileEye** vision-based advanced driver assist systems chips capable of 176 trillion ops per second with 12 RISC-V CPU cores.

- Andes ISO 26262 Functional Safety ASIL D Dev Process Certification for RISC-V embedded automotive safety with Andes processors

- **Renesas and SiFive** partner on next-gen, highend RISC-V automotive applications. SiFive will license their RISC-V core IP to Renesas.

- **Imagination Technologies** GPU linked by a RISC-V core for ASIL-B level designs with ISO 26262 safety critical certification.

- **IAR Systems** extended functional safety of its Embedded Workbench sw tool chain to the RISC-V core of NSITEXE, subsidiary of automotive leader Denso.

- **Europe GaNext** simplifies power converters with GaN power semiconductors with better efficiency and compactness for EV chargers.

2020 RISC-V automotive opportunity 4M cores; growing to 150M cores in 2022 and 2.9B cores by 2025. – Deloitte, December 2021

RISC-V Automotive Value Multicore SoC revenue to be \$5.7B in 2022. Advanced RISC-V AI SoCs for High-End Passenger Cars to Reach \$819M by 2027

#### RISC-V-based AI SoCs will grow **73.6% CAGR to 25B units and \$291B in revenue by 2027** – Semico Research, December 2021

- Alibaba Cloud tops MLPerf Tiny v0.7 Benchmark with its IOT processor

- **Esperanto** accelerating ML Recommendation With Over 1,000 RISC-V/Tensor Processors on ET-SoC-1 Chip

- **StarFive** released the world's first RISC-V AI visual processing platform

- **Andes** released superscalar multicore and L2 cache controller processors.

- **NVIDIA CUDA** support on Vortex RISC-V GPGPU enables scaling from 1-core to 32core GPU based on RV32IMF ISA

RISC-V®

- **E4** Monte Cimone Cluster along with DEI-UNIBO contributing to architecture, software, and integration.

- **European Processor Initiative** RISC-V accelerator with first chip Sep 2021

- **Technical University of Munich** (TUM) quantum cryptography chip for quantum computing security demands

erformance

- **Tactical Computing Labs** HPC-centric software test suite for GCC and LLVM

- **Cortus** is developing a high-performance RISC-V Out-of-Order processor core for the European eProcessor project.

- **De-RISC** HW-SW platform for multi-core RISC-V SoC for safety critical aerospace

### Introduction to Vector on RISC-V

## **RISC-V Vector (RVV)**

At the end of 2021, RISC-V International ratified version 1.0 of the Vector Extension

- Single RISC-V Extension

- Variable Vector Lengths

- Maps into existing neural network models (multiple maps)

- Allows for small code size and low power consumption

- Range of vector data types and sizes

- Enables open-source extensions

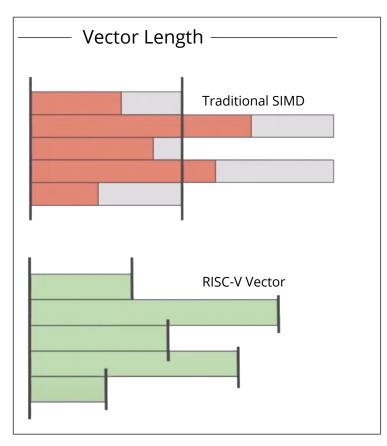

### **RISC-V Vectors vs Traditional SIMD**

- Variable Vector Register Length

- Vector width configurable at runtime

- Up to maximum hardware length (VLEN)

- Vector ISA is agnostic to VLEN

- Unified Code Base

- ARM has two different ISAs (Helium & Neon)

- IA-32 vector instructions were an order of magnitude larger when supporting SIMD vector lengths

- No requirement for dedicated vector data memory

|                                     | RVV             | ARM SVE                 | x86 AVX512                  |

|-------------------------------------|-----------------|-------------------------|-----------------------------|

| Spec supports multiple vector sizes | Yes             | Yes                     | No                          |

| VL register                         | Yes             | No                      | No                          |

| Masks                               | Yes (1)         | Yes (16)                | Yes (8)                     |

| Narrowing/Widening                  | Yes, LMUL       | Yes, 2 instructions     | Yes, 2 instructions         |

| Mixed Datatype Vectorization        | Uses LMUL       | Pack/Unpack             | Pack/Unpack                 |

| Hardware Unrolling (LMUL)           | Yes             | No                      | No                          |

| Polymorphic Encoding                | Yes, vtype      | No                      | No                          |

| Strided Memory Access               | Yes             | No                      | No                          |

| Gather/Scatter                      | Yes             | Yes                     | Yes                         |

| Structured/Segmented Loads          | Yes             | Yes                     | No                          |

| Forward Progress on gather/scatter  | Vstart          | Repeat full instruction | Mask state                  |

| Fixed Point Support                 | Yes             | Partial                 | No                          |

| Complex Support                     | No              | Yes                     | Partial                     |

| Reductions                          | Yes             | Yes                     | No                          |

| Register Gather                     | Yes             | Yes                     | No                          |

| Tail Element control                | Merge, Agnostic | Merge, Zeroing          | Merge, Zeroing <sup>o</sup> |

| Destructive destination             | No              | Yes                     | No 17                       |

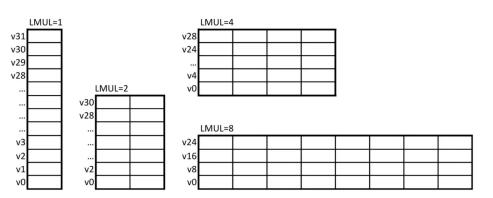

# LMUL - Multiplying Vector Length

- LMUL parameter that multiplies the number of VLEN registers operated on by each instruction

- Goal Fewer Instructions

- Large vector data computations

- More efficient parallel computation (both scalar & vector)

- Smaller code size, fewer memory accesses

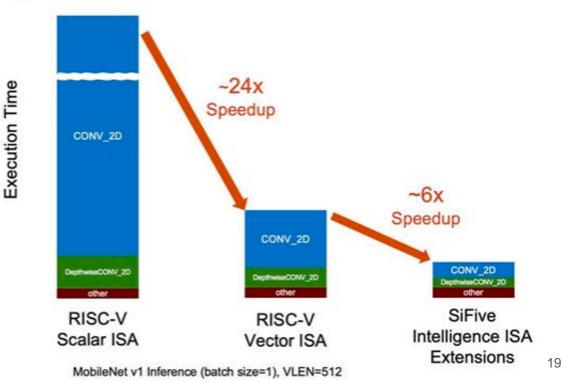

### **RISC-V Custom Extensions**

#### SiFive Intelligence Extensions Accelerate End-to-End Models

- Reserved opcode space for custom extensions

- Allows for layering of value-add custom extensions (open-source or proprietary)

- Flexibility to push the boundaries

- Cost effective model for R&D

### The Future of AI & RISC-V

## Vector SIG

ML: <u>https://lists.riscv.org/g/sig-vector</u>

Charter/Docs: <a href="https://github.com/riscv-admin/vector">https://github.com/riscv-admin/vector</a>

- Finishing Zvfh / Zvfhmin extensions & tests

- Aligning efforts around Packed SIMD extension

- Matrix Multiplication extension

# **Floating Point SIG**

Chair: Kenneth Rovers, Imagination Technologies ML: <u>https://lists.riscv.org/g/sig-fp</u> Charter/Docs: <u>https://github.com/riscv-admin/fp</u> Goals:

- New FP formats and operations

- Move beyond IEEE-754 standard, Zfh/Zfhmin, Vector

- Develop the strategy, gaps, and prioritizations for FP & RISC-V

# bfloat16 Task Group

Chair: Ken Dockser, Rivos

ML: <u>https://lists.riscv.org/g/sig-fp</u>

Charter/Docs: <a href="https://github.com/riscv-admin/bfloat16">https://github.com/riscv-admin/bfloat16</a>

Specification: <a href="https://github.com/riscv/riscv-bfloat16">https://github.com/riscv/riscv-bfloat16</a>

- Extensions for vector and scalar floating-point

- Includes BF16 format and behaviors

- Basic instructions allowing BF16 as an interchange format

- FP #'s converted between BF16 and other formats like single precision, FP32

- Add widening multiply-add type instructions (BF16 operands, FP32 result)

- Note: more instructions to come...

### **Software Committees**

#### **Platforms definition**

#### Platforms standardization

- Binary compatibility

- Source-code compatibility

ABIs and Firmware Services Bootstrap and Secure Boot Unified Discovery

Reduce the risk in adopting RISC-V

Standardize solutions Reach consensus and document other ideas Avoid fragmentation

Drive enablement and optimization Own and coordinate efforts Enable innovation/differentiation

#### Toolchains and development tools

(Software) applications enablement

- Compilers and Debuggers

- Optimized runtime libraries

- Code-speed and code-size

Managed Runtimes Simulators and Performance Models

#### Attract applications to RISC-V

# Coming in 2023

- RISC-V Vector C intrinsics Task Group

- AI/ML Special Interest Group

- Vector SIG

- Matrix Multiply

- Vector Phase 2

- LLVM Improvements

- intrinsics

- autovectorization

- oneAPI Engagement

- oneDNN

- OpenMP®

- OpenCL<sup>™</sup>

- SYCL<sup>™</sup>

### How can you get involved in AI and RISC-V?

## **RISC-V Technical Community**

RISC-V°

- **GitHub** <u>https://github.com/riscv</u>\*

- Mailing Lists

<a href="https://lists.riscv.org">https://lists.riscv.org</a>

- RISC-V Wiki

<u>https://wiki.riscv.org</u>

- Groups

https://lists.riscv.org/g/sig-

<u>ai-ml</u>

https://lists.riscv.org/g/sig-fp https://lists.riscv.org/g/sig-vector

stephano@riscv.org